Master VLSI Design with Real Tools & Tracks

From RTL design to UVM verification — build, debug, and level up with visual tools, waveforms, and real interview prep.

Structured Learning Paths

Follow curated learning journeys designed by industry experts. Track your progress, meet prerequisites, and level up systematically.

Guided Learning

Step-by-step progression with clear prerequisites and milestones

Progress Tracking

Visual progress indicators and completion analytics

Achievement System

Earn points, unlock achievements, and showcase your expertise

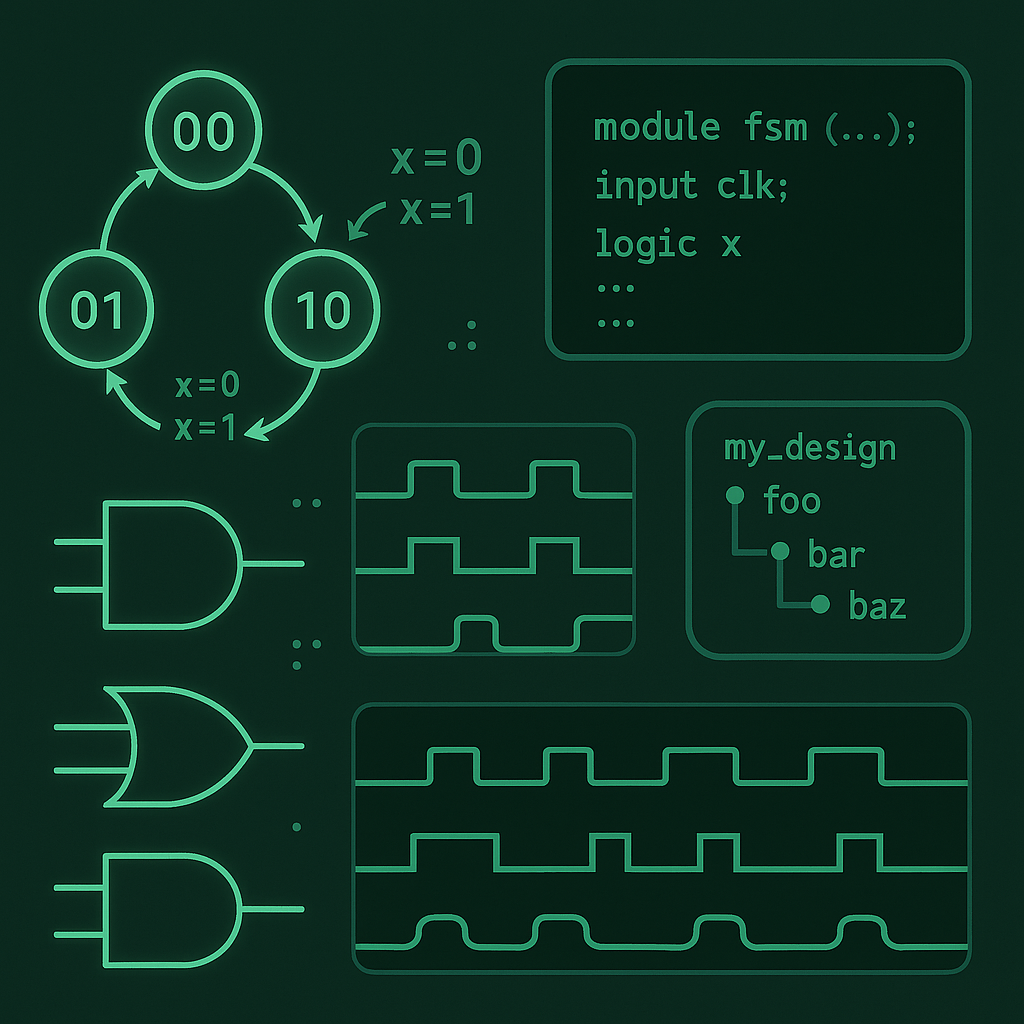

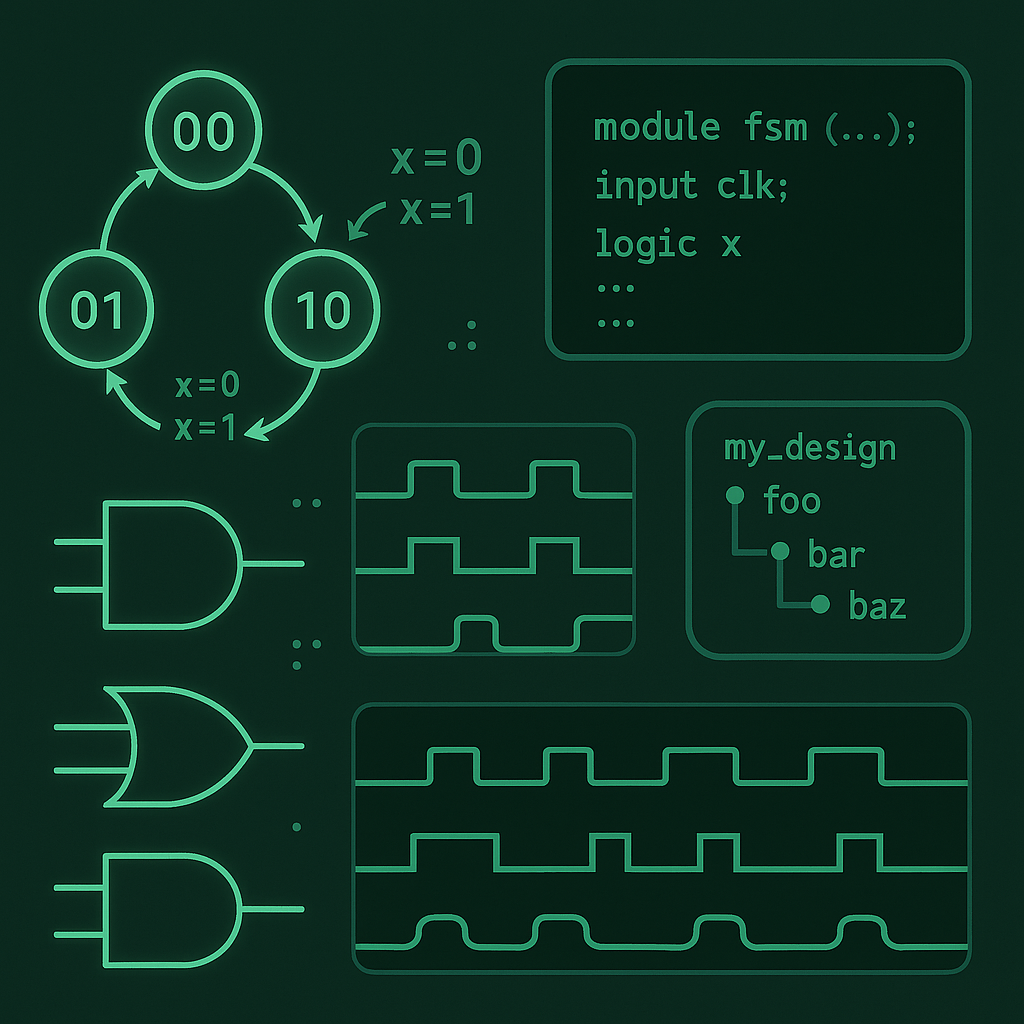

RTL Design Track

Master RTL design using SystemVerilog. Build FSMs, logic blocks, and run simulations.

- Combinational and sequential design

- FSM design and datapath control

- Clock domain handling

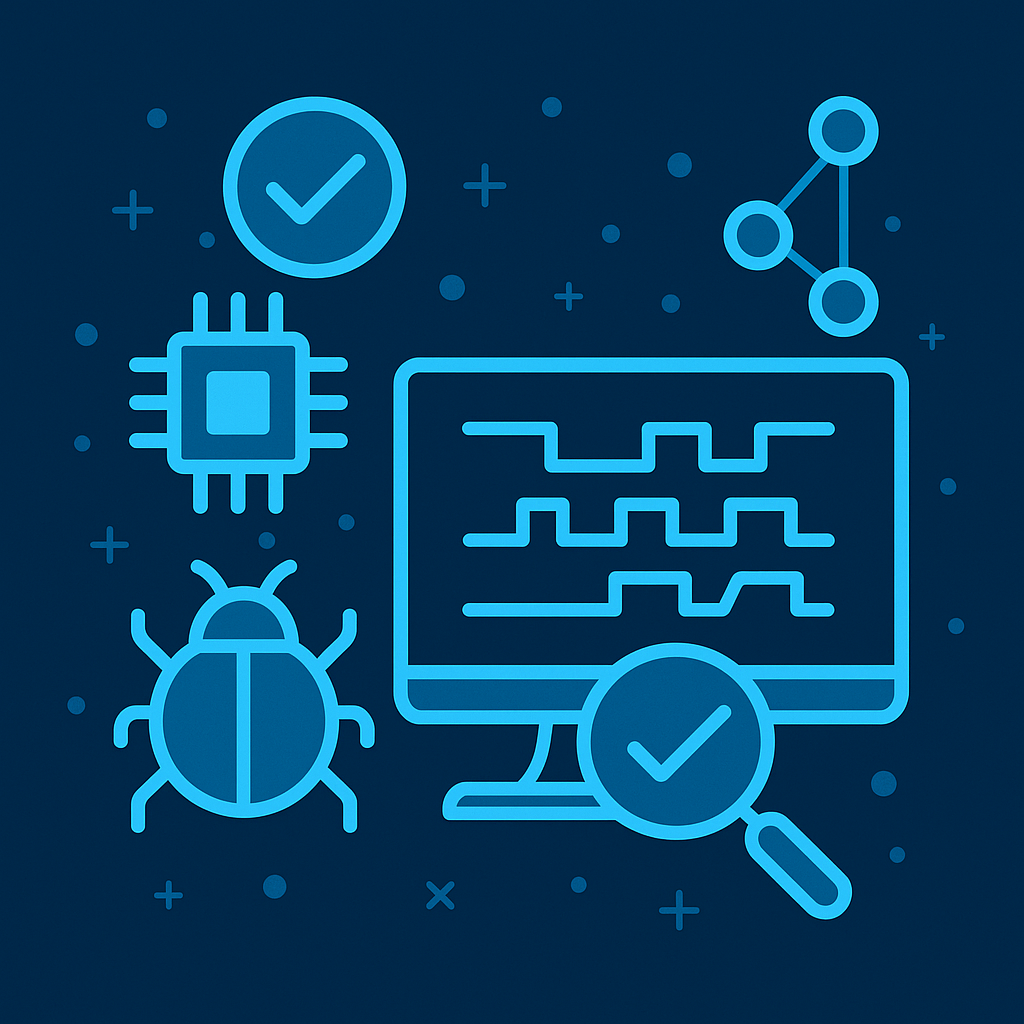

Design Verification Track

Write UVM testbenches, assertions, and validate digital designs.

- UVM Testbench structure

- Constraint-random and sequences

- Assertions and functional coverage

Community Open Source Projects

Join a global community building reusable IPs, verification libraries, and tools for learning and industry use.

- Collaborate on RTL IP and SoC designs

- Contribute verification agents, checkers, and coverage models

- Build, share and review tools for simulation and debug

- Build and maintain open reference designs together

AI in VLSI

Explore how Artificial Intelligence is transforming chip design, verification, and optimization workflows.

- Machine learning for faster verification and bug detection

- AI-driven RTL design optimization and power analysis

- Automated test generation and coverage closure

- Predictive analytics for yield and reliability improvement

Protocols & Interconnects

Master industry-standard communication protocols essential for modern SoC and chip design.

- AMBA protocols (AXI4, AHB, APB) for SoC interconnects

- High-speed serial interfaces (PCIe, USB, SATA)

- Memory interfaces (DDR4/5, LPDDR, HBM) and controllers

- Networking protocols (Ethernet, CXL) and security interfaces

Why DenseChip?

Experience the most comprehensive VLSI learning platform with cutting-edge tools and community support

Smart Topics

Organized by tags, topics & difficulty. From UVM to assertions.

Track Progress

Focus on your weak areas with stats, coverage & timeline.

Community

Comment, discuss, and collaborate with other learners.

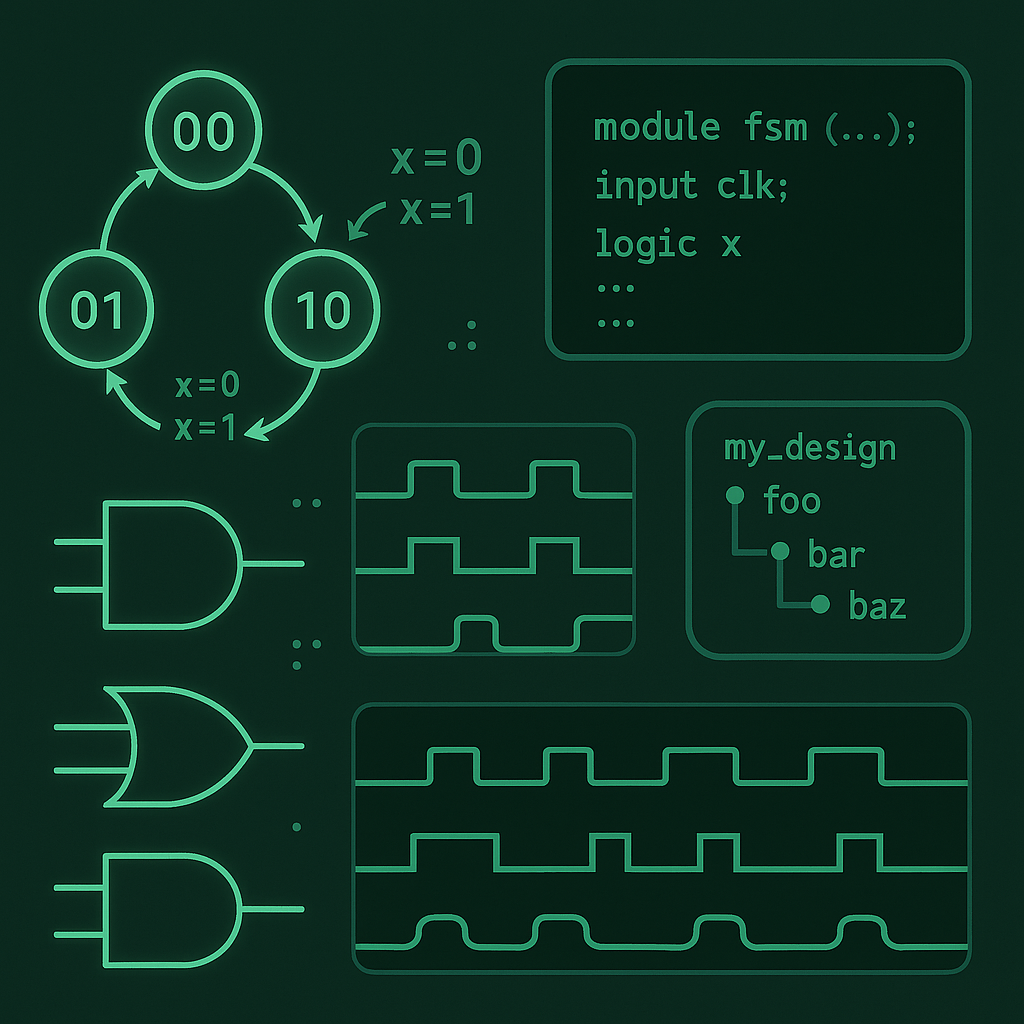

Assertion Waveform Viewer

Trace assertion firing/failure, zoomable timeline, and visual sequence preview.

Interface Connectivity Explorer

View port bindings, color-coded paths, and hierarchical graph layouts.

UVM Blueprint Tool

Auto-detect UVM testbench, explore hierarchy, and zoomable views.